2重PLL同期検波によるDirect Conversion FMラジオ-2

■概要

Receiver 3.1で、Xtal発振を参照して自励発振のVCOを制御するの第1のPLLループと、そのXtalによるVCXOの発振周波数を制御する第2のPLLループを持つ2重PLL回路が、ループの応答特性に差をつければ特別な配慮をしなくても動作する可能性があることを報告しました。

それを実証しようと思い基板を組んだところ、PLLが発振状態というのでしょうか、安定しません。

そこで特許2859037の請求項1を試したところ、見事ロック。

さすが特許になっただけのことはあると実感しました。

■基本回路

2重PLLの回路構成は2種類あります。

第2の方式は第1のVCOを可変分周し、第2のVCOの周波数を固定にして、第1の位相比較回路に入力するものです。

いずれの方式においても、R3が特許のポイントで、この抵抗がないとPLLが発振してしまいます。■目標規格

1.受信周波数:80MHz~93MHz

2.選局:VRによる連続可変

3.感度:-75dBm(S/N=40dB@40kHz dev)

弱電界のLock外れと強電界PLL発振はともにまだ性能不十分で、さらなる検討を要します。

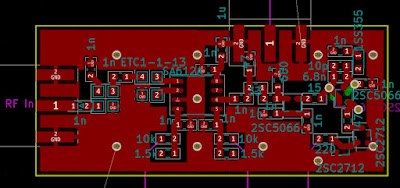

■回路図

ブレッドボードレベルですが、第1方式の回路です。

出力の一方をµPB571Cで64分周します。

5Vで13MHz変化なので、VCOのKファクターは2.6MHz/Vになります。

もう一方の出力は第1の位相比較回路に入力します。

(2)第2のVCOはOP AmpとCRで構成し、VRで発振周波数を80MHz~93MHzの1/64の1.25~1.45MHz変化させ、さらにVari-Capで5Vで約3KHz程度変化させます。

この3KHzはとりあえず実験的に決めた値です。

64倍して受信周波数に換算すると約200KHzになり、FM放送の最大周波数偏移を考えるとまあ妥当かなと思います。

したがってKファクターは40KHz/Vです。

このVCOはCMOS Gateのシュミットトリガで構成することもできますが、周波数の電源電圧変動が大きいのでOP Ampのシュミットトリガにしました。

(3)第2の位相検波回路はµPD2833Cで、レベルアップした64分周出力と第2のVCO出力を位相検波しチャージポンプとループフィルタを経由して第1のVCOのVari-Capに帰還します。

µPD2833Cの位相検波回路は入力波形のDutyを50:50に、また立上がりと立下りを急峻にしないと完全な動作が期待できないようでしたので、VとR の前にInverterを挿入しました。

(4)最後に特許に従って、第1のループフィルタの出力を第2のループフィルタに抵抗を介して印加します。

(5)「PLL同期検波によるDirect Conversion FMラジオ-1(修正版)」で、S/Nを不問とすれば感度はキャプチャーレンジで決まり、キャプチャーレンジはVCOのKファクターに依存することを報告しました。

Dual PLLのキャプチャーレンジは、OP AmpのDC Gainとループフィルター特性が同じであれば、第2のVCOのKファクターで決まると考えられます。

上記のように40KHz/Vなので「PLL同期検波によるDirect Conversion FMラジオ-1(修正版)」を参考にすればLNAなしで-50dBm程度ということになります。

■受信の動作確認

とりあえず「PLL同期検波によるDirect Conversion FMラジオ-2」のRF基板+ブレッドボードに組んでみたところ、確かにLNAなしで-50dBm程度の感度になりました。

ところがRF入力が-30dBm以上で、PLLが発振のような状態になり、受信不能なりました。

そこで特許2859037の請求項2に従って、上記回路図のR12とR20をCut&Tryして、各ループフィルター電圧の加算比を変えてみたところ確かに改善しました。

とりあえずLNAを前置して、感度を測定しました。

弱電界のLock外れと強電界PLL発振はともにまだ性能不十分で、さらなる検討を要します。