PLL同期検波によるDirect Conversion FMラジオ-2

■概要

Receiver 3.2で、LNA込みの感度は少なくとも-90dBmが期待できると報告しました。

ただ感度アップすると、VCOの出力がアンテナやLNA・Mixerの入力に飛び込み、PLLが自分自身のVCOにロックしてしまうという本質的な問題に突き当たります。

IQ復調によるDirect Conversionでは、この問題はDCオフセットとして有名ですが、PLLでは自分自身にロックしてしまうという現象になります。

そこで実際にFMラジオを組んでみて、どうしたら安定に動作するかを検証します。

■目標仕様

1.受信周波数:75MHz~95MHz

2.感度:-90dBm (S/N:40dB@40kHzdev)

3.選局:VRによる連続可変

4.Capture/Hold Range:±100KHz

■基本設計

このFMラジオ基板はFMラジオ-1のSimulationと同じ構成です。

位相検波回路にSA612Aを使い、誤差出力をOPアンプ(NJU77701F)で増幅してVCOに帰還します。

FM出力は誤差増幅回路の出力からディエンファシス回路を経由して得ます。

VCOはSA616Aのコルピッツ発振回路を使ったところ、まさに発振出力がMixerに回り込んでしまったので、やむなく外付けにしました。発振回路は「広帯域VCO」の稿で述べた正帰還形発振回路です。

周波数は電流制御とし、選局VRの電流と誤差制御回路の出力電流を加算します。選局VRは75MHz~95MHzをカバーし、誤差制御回路の出力で±500kH変化させます。

基本回路(LNAなし)を下記に示します。

選局の電圧Vcを0~5V変化させた時の発振周波数が下記です。

■回路図

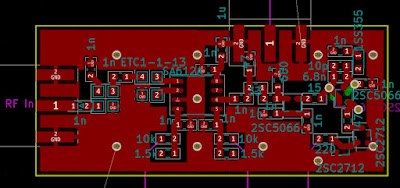

■基板

自作両面基板なので、部品面と裏面ベタアースのスルーホールが十分とれません。できるだけ多く基板の裏表を半田で接続することにします。

基板は高周波部のみで、OPアンプとAF部は別基板です。(略)

■感度測定

ディエンファシス回路はありません。

-90dBmまで順調ですが、-95dBmになるとロックが外れ気味になります。

また-20dBmではPLLが不安定になります。

参考程度ですが、感度は約-80dBm (S/N:40dB@40kHzdev)となりました。また最大S/Nは35dBで、これは受信周波数範囲に対して変調周波数偏移が小さいためと考えます。

■まとめ

FM放送を受信するために2/λダイポールアンテナ接続すると、基板むき出しの場合、VCO出力がアンテナに飛び込んで安定した動作を得られませんでした。

安定した動作が得るためには、すべての基板をアルミのシールドケースに収めなければなりませんでした。

シールドケースがあれば、そこそこの音質で受信できました。

またLNAを前置したところ、シールドケースがあっても安定した受信ができませんでしたので、今のところLNAなしで受信しています。

0 件のコメント:

コメントを投稿